Audio on ZedBoard

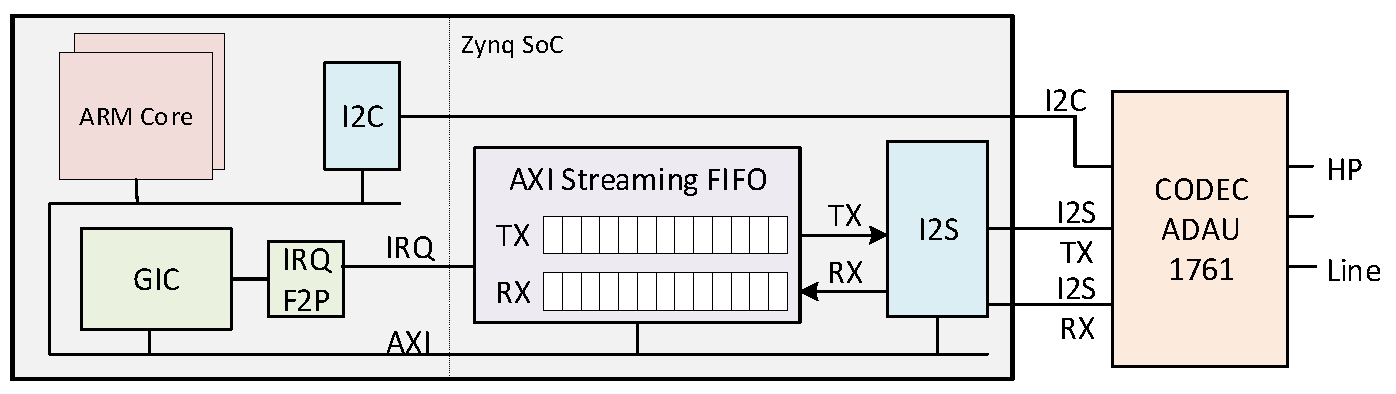

The figure below shows the audio setup on the Zedboard. An external codec (ADAU1761) is connected both via I2C and I2S. I2C is directly connected to a processor peripheral generating the I2C protocol. I2S is connected to an I2S controller (axi_i2s_adi) in the programmable logic side. The I2S controller interfaces via two AXI streaming interfaces with a AXI Streaming FIFO. The AXI streaming FIFO offers MMRs to manipulate the FIFOs (TX and RX) via the AXI bus from the processor. It also has an interrupt to signal to the processor.

Audio samples inserted into the AXI FIFO are transmitted by the I2S controller to the CODEC, which converts them into analog audio signals. The CODEC in this chain controls the sampling frequency. Conversely, the path has a fixed data configuration. The AXI FIFO expects samples as 32-bit words interleaved stereo. This means, the first 32-bit word is the first sample for the left channel, the second 32-bit word is the first sample for the right channel. While the AXI FIFO has a 32-bit interface, the CODEC operates on 24 bits. The CODEC interprets the upper 24 bits; the lower 8 bits are ignored.

The AXI Stream FIFO has the following HW configuration (defined upon HW synthesis). Both transmit and receive paths are configured identical. Note that the FIFO operates in cut through mode (see manual for description).

| Property | Value |

|---|---|

| Base Address | 0x41630000 |

| Cut Through | Enabled |

| FIFO Depth | 1024 |

| Programmable Full Threshold | 512 |

| Programmable Empty Threshold | 10 |

AXI FIFO HW Configuration